# **High Frequency AC Regulator for Non-linear Loads**

C. A. Petry, J. C. Fagundes and I. Barbi

Power Electronics Institute - INEP

Dept. of Electrical Engineering - EEL

Federal University of Santa Catarina – UFSC

P. O. box 5119 – 88040-970 – Florianópolis – SC- Brazil

petry@inep.ufsc.br, fagundes@inep.ufsc.br and ivobarbi@inep.ufsc.br

Abstract – This paper presents a new high frequency AC voltage regulator, to provide energy to linear and non-linear loads. The proposed regulator can also operate as an active filter, correcting the distortions from the input AC voltage and providing a low harmonic distortion AC output voltage. Principle of operation, theoretical analysis and simulation results are shown. Laboratory experimental results are also presented, which demonstrate the feasibility of the study carried.

#### 1 Introduction

The use of voltage regulators has been spreading in all of the areas that involve the use of electronic equipments, as residential, commercial or industrial areas. So, the national industry has been trying to fulfil this potential market with simple and reliable solutions.

There are several topologies, already dominated, available to industrial factoring. Basically, those topologies can be classified into two groups: Serials and Non-serials. The first ones [1], [2], [3] and [4] present the great advantage of processing only a percentage of the load power, acting in truth as a compensator. However, in most cases, they are not isolated. The second ones [5, 6] process the total load power and in most cases they are isolated. Trying to make the commutation better, topologies without dead time [7] and with soft switching [8, 9] were developed. The disadvantage of the last ones is the great number of active switches.

There is no known information regarding topologies that join simplicity, high efficiency and capability to provide energy to non-linear loads. Also, there is a lack of topologies that can operate simultaneously as a regulator and as an active filter.

This paper presents a new topology, that can provide energy to non-linear loads, isolate the load from the AC line voltage and act as an active filter using only two active switches and presenting high efficiency.

# 2 THE PROPOSED TOPOLOGY AND PRINCIPLE OF OPERATION

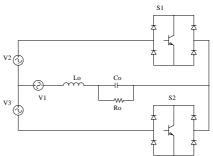

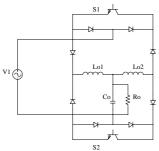

The topology presented in [1] and shown in Fig. 1, in its simplified form, has a good static gain, is isolated and allows to correct positive and negative variations of the input voltage. However, this topology, due to the presence of dead time, needs the use of snubbers, resulting in low efficiency. The topology presented in [7] and shown in Fig. 2, eliminates the dead time problem, solving the matter of high voltage across the components. However, this structure is not isolated and does not allow the increment of the output voltage.

Fig. 1 – Topology proposed in [1].

Fig. 2 – Topology proposed in [7].

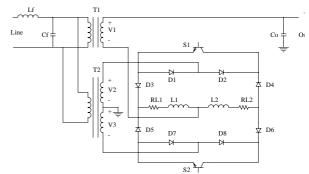

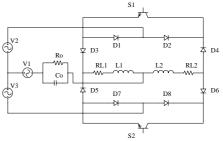

In Fig. 3 the proposed topology is shown. In order to simplify the description of the operation stages, a simplified topology is adopted, as shown in Fig. 4.

Fig. 3 – Proposed topology.

Fig. 4 – Proposed topology simplified.

The inductors  $L_1$  and  $L_2$ , and the capacitor  $C_o$ , constitute the output filter. The resistances of the filtering inductor's windings are represented by  $R_{L1}$  and  $R_{L2}$ . The inductor  $L_f$  and the capacitor  $C_f$  form the input filter. The load is represented by  $R_o$ . Actually, this load is non-linear and is constituted by a rectifier with a capacitive filter.

In order to describe the operation of the circuit, it is assumed that:

- The power switches are ideal;

- During a switching period, the input and output voltages are considered constant, because the switching frequency (F<sub>s</sub>) is considerably higher than the line frequency (F<sub>r</sub>);

- The load is purely resistive.

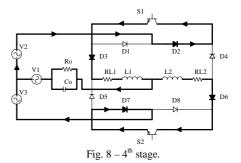

The operation stages are as follows:

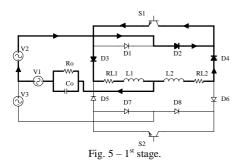

<u>1</u><sup>st</sup> stage (t<sub>0</sub>, t<sub>1</sub>), (Fig. 5):  $S_1$  is in ON state. The load current flows through  $V_1$ ,  $V_2$ ,  $D_2$ ,  $S_1$ ,  $D_3$ ,  $R_{L1}$ ,  $L_1$  and  $R_0//C_0$ . The current i<sub>L2</sub>, through inductor  $L_2$ , flows through  $L_2$ ,  $R_{L2}$ ,  $D_4$ ,  $S_1$ ,  $D_3$ ,  $R_{L1}$  and  $L_1$ . During this stage energy is transferred from  $V_1$  and  $V_2$  to the load. This stage is finished at time  $t_1$ , when  $S_2$  is commanded to turn-on.

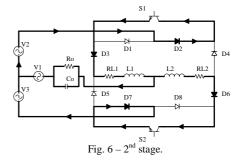

$2^{nd}$  stage (t<sub>1</sub>, t<sub>2</sub>), (Fig. 6): This stage starts when S<sub>2</sub> is turned-on. The switches S<sub>1</sub> and S<sub>2</sub> are ON. The current through inductor L<sub>1</sub>, i<sub>L1</sub>, flows through V<sub>1</sub>, V<sub>2</sub>, D<sub>2</sub>, S<sub>1</sub>, D<sub>3</sub>, R<sub>L1</sub>, L<sub>1</sub> and R<sub>o</sub>//C<sub>o</sub>. The current through inductor L<sub>2</sub>, i<sub>L2</sub>, flows through L<sub>2</sub>, R<sub>L2</sub>, D<sub>6</sub>, S<sub>2</sub>, D<sub>7</sub>, V<sub>3</sub>, V<sub>1</sub> and R<sub>o</sub>//C<sub>o</sub>. The load receives energy from V<sub>1</sub>, V<sub>2</sub> and V<sub>3</sub>. This stage is finished when S<sub>1</sub> is ordered to turn-off, at time t<sub>2</sub>.

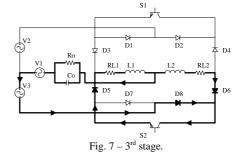

$3^{rd}$  stage (t<sub>2</sub>, t<sub>3</sub>), (Fig. 7): At time t<sub>2</sub>, when S<sub>1</sub> is switched-off, the third stage begins. The switch S<sub>2</sub> is in the ON state. The load current flows through V<sub>1</sub>, V<sub>3</sub>, D<sub>8</sub>, S<sub>2</sub>, D<sub>5</sub>, R<sub>L1</sub>, L<sub>1</sub> and R<sub>o</sub>//C<sub>o</sub>. The current i<sub>L2</sub> flows through L<sub>2</sub>, R<sub>L2</sub>, D<sub>6</sub>, S<sub>2</sub>, D<sub>5</sub>, R<sub>L1</sub> and L<sub>1</sub>. The load receives energy from V<sub>1</sub> and V<sub>3</sub>. The voltage applied across the load is the difference between V<sub>1</sub> and V<sub>3</sub>. This stage is finished at time t<sub>3</sub> when the switch S<sub>1</sub> is commanded to turn-on.

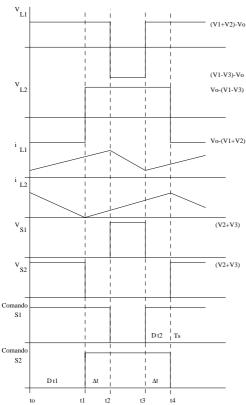

The main idealized waveforms, for a switching period, considering the input voltage in its peak value, are shown in Fig. 9.

## 3 ANALYTICAL STUDY

The input voltages of the power stage are sinusoidal, obtained from the secondary windings of two transformers. The transformation ratios are  $n_1$ , for transformer  $T_1$ , and  $n_2$  and  $n_3$ , for transformer  $T_2$ . The voltages  $V_1$ ,  $V_2$  and  $V_3$  are given by expressions (1), (2) e (3), respectively.  $V_{in\_p}$  is the voltage peak value of the AC line.

$$V_1(t) = n_1 \quad V_{in-p} \quad \sin(\omega t) \tag{1}$$

$$V_2(t) = n_2 \quad V_{in_p} \quad \sin(\omega t) \tag{2}$$

$$V_3(t) = n_3 \quad V_{in_p} \quad \sin(\omega t) \tag{3}$$

To determine the static gain of the power stage, it will be neglected the stages where both switches are ON, that means, the intervals  $\Delta t$  in Fig. 9. These intervals are very small, if compared with a switching period, so its influence in the static gain can be neglected.

The ON intervals of the switches  $S_1$  and  $S_2$  are given by expressions (4), (5) and (6).

Fig. 9- Main waveforms for a switching period.

$$\Delta t = (t_2 - t_1) = (t_4 - t_3) \tag{4}$$

$$\Delta t_1 = t_1 - t_{0 \approx}(t_1 - t_0) + 2\Delta t \tag{5}$$

$$\Delta t_2 = t_3 - t_{2\cong} T - \Delta t_1 \tag{6}$$

The static gain is given by expression (7) as a function of the voltages in the secondary side of transformers  $T_1$  and  $T_2$ , and by expression (8) as a function of the input voltage and the transformation ratios of  $T_1$  and  $T_2$ :

$$Vo = V_1 - V_3 + (V_2 + V_3)D \tag{7}$$

$$Vo = V_{in} [n_1 - n_3 + (n_2 + n_3)D]$$

(8)

The current ripple through inductors  $L_1$  and  $L_2$  is given by expressions (9) and (10), respectively:

$$\Delta i_{L1_{\text{max}}} = \frac{(V_1 + V_2) - V_o}{L_1 F_s} D_{\text{max}}$$

(9)

$$\Delta i_{L2\text{max}} = \frac{V_o - (V_1 - V_3)}{L_2 F_s} (1 - D_{\text{max}})$$

(10)

The expression that determines the voltage ripple over the capacitor  $C_0$  is given by (11):

$$\Delta V_{Co_{\text{max}}} = \frac{4}{\pi^3 F_s^2 C_o L_o}$$

$$\begin{bmatrix} V_o - (V_1 - V_3) + \\ (2V_1 + V_2 - V_3 - 2V_o) D_{\text{max}} \end{bmatrix}$$

(11)

The transfer function of the circuit, necessary to design the compensator, is given by expression (12), neglecting the series resistances of the output capacitors.  $V_s$  is the maximum value of the ramp voltage in the generation of the PWM command signals.

$$G(j\omega) = \frac{V_o(j\omega)}{V_C(j\omega)} = \frac{(V_2 + V_3)}{V_S} =$$

$$= \frac{1}{(j\omega)^2 L_o C_o + (j\omega) \frac{L_o}{R_o} + 1}$$

(12)

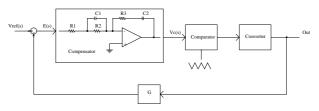

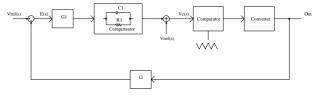

A compensator, which diagram is shown in Fig. 10, is designed using the classical structure, normally used for Forward converters [10]. Another possibility, considering a sliding mode control was used [12, 13]. The corresponding diagram is shown in Fig. 11.

Fig. 10 - Conventional system control.

Fig. 11 - Sliding mode control.

#### 4 SIMULATION RESULTS

In order to demonstrate the operation of the proposed topology and to validate the mathematical expressions previously presented, the circuit shown in Fig. 4 has been simulated, with closed loop operation and a PWM modulation. The used parameters values were:

$V_1(t) = 311V$  (Peak value);

$V_2(t) = 120V$  (Peak value);

$V_3(t) = 70V$  (Peak value);

$V_o = 311V$  (Peak value of the output voltage);

$n_1 = 1$  (Transformation ratio of  $T_1$ );

$n_2 = 0,386$   $n_3 = 0,225$  (Transformation ratio of T<sub>2</sub>);

$P_o = 1kW$  (Output power);

$L_1 = L_2 = 100 \mu H$  (Filter inductors);

$R_{L1} = R_{L2} = 3,6 m\Omega$  (Series resistance of the filter inductors);

$C_o = 100 \mu F$  (Output capacitor);

$R_o = 10 k\Omega$  (Output resistance, in parallel with a non linear load of 1 kW);

$F_r = 60 \, Hz$  (Line frequency);

$F_s = 20 kHz$  (Switching frequency);

$\Delta t = 500 \, ns$  (Simultaneous conduction time of S<sub>1</sub> and S<sub>2</sub>).

The transformation ratio of  $T_2$  was obtained by simulation, as a function of the voltage drops on the circuit components, aiming to optimise the performance of the control circuit. The transformation ratio of  $T_1$  is one, because the transformer  $T_1$  is used only to isolate the load from de AC line.

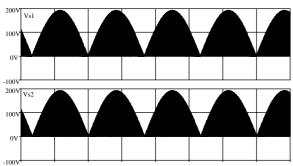

In Fig. 12 the voltage across the switches are presented and it can be observed that they have a good behaviour, without voltage spikes.

Fig. 12 - Voltage across switches  $S_1$  and  $S_2$ .

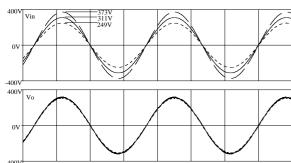

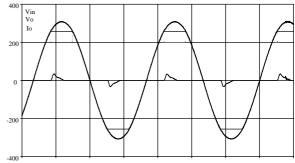

In Fig. 13 the output voltage is shown with the converter operating at minimal, nominal and maximum input voltage. This simulation was done with linear load and a sliding mode controller. The output voltage has a good regulation when a variation of  $\pm$  20% of the input voltage is considered.

Fig. 13 – Output voltage for three different input voltages.

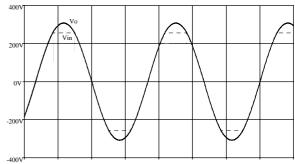

In Fig. 14 the output voltage is shown with the converter operating with distorted input voltage, that is, with high harmonic content. It can be verified that the converter as an active filter behaviour.

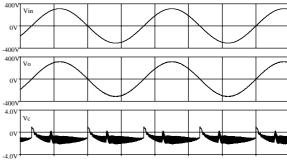

In Fig. 15 the converter's output voltage is shown with non linear load. In this case the input voltage is considered purely sinusoidal. It is also shown in Fig. 15 the controller's output voltage. It can be seen that the output voltage has a low harmonic content, with a waveform without overvoltages.

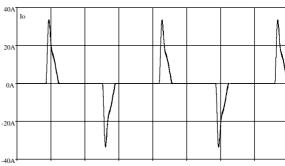

The non linear load's current is shown in Fig. 16.

In Fig. 17 the simulation results for non linear load with distorted input voltage are shown. It can be noted the good quality of the waveforms of output voltages, showing the

good performance of this topology when operating as active filter an voltage regulator.

Fig. 14 – Output voltage with distorted input voltage.

Fig. 15 - Output voltage for non linear load.

Fig. 16 - Current through non linear load.

Fig. 17 – Output voltage for non linear load with distorted input voltage.

# 5 EXPERIMENTAL RESULTS

In order to verify experimentally the principle of operation, some tests were made on a 1 kW prototype providing energy to a linear and to a non linear load.

The power semiconductors used on the prototype were:

- S<sub>1</sub> and S<sub>2</sub> IRG4PSC71U from IR;

- D<sub>1</sub> to D<sub>8</sub> HFA30PA60C from IR.

To eliminate the influence of the leakage inductance of  $T_1$  and  $T_2$  a small RC clamper, in parallel with  $S_1$  and  $S_2$ , was used. The other components are similar to those shown in Section four.

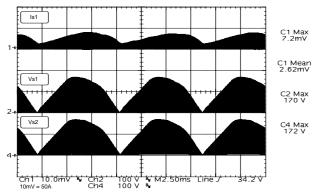

In Fig. 18 the voltage across the switches is presented and it can be observed that they have a good agreement with the simulation results. The current through the switch  $S_1$  is also shown in Fig. 18.

Fig. 18 – Voltage across switches  $S_1$  and  $S_2$  and current through the switch  $S_1$ .

In Fig. 19 the details of the voltages across switches  $S_1$  and  $S_2$  and the current through the switch  $S_1$  are shown.

Fig. 19 – Detail of the voltage across switches  $S_1$  and  $S_2$  and current through the switch  $S_1$ .

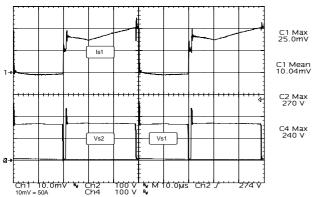

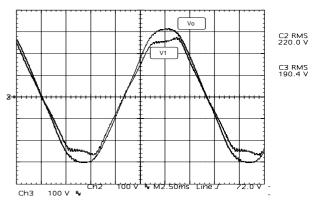

In Fig. 20 the output voltage for a linear load is shown. The control system used in that test was a conventional PID compensator.

Fig. 21 shows the output voltage for linear load with sliding mode control. It can be observed that the output voltage has a good quality and small harmonic distortion. The voltage  $V_1$  is the output voltage of the transformer  $T_1$ .

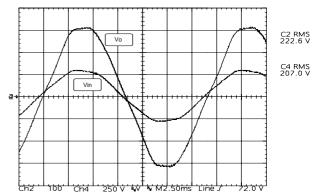

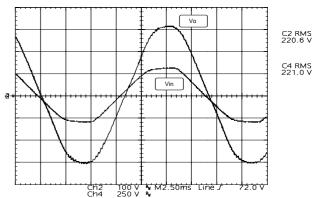

In Fig. 22 the output voltage for linear load and the AC line voltage are shown. The output voltage has a low harmonic content, showing that the converter acts as an active filter.

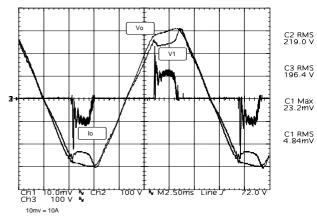

Fig. 23 shows the output voltage for non linear load with sliding mode control. The low quality of output voltage is caused by the leakage inductance of transformers  $T_1$  and  $T_2$ . In order to obtain better quality of output voltage, those transformers ( $T_1$  and  $T_2$ ) must be built using techniques for reduction of leakage inductance and of windings resistances.

Fig. 20 – Output voltage for linear load with conventional control system.

Fig. 21 – Output voltage for a linear load with sliding mode control.

Fig. 22 - Output and AC line voltage for linear load.

Fig. 23 – Output voltage for a non linear load with sliding mode control.

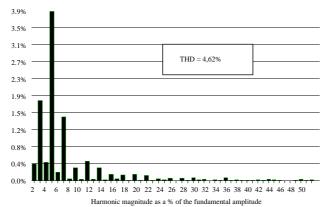

In Fig. 24 the harmonic spectrum of the output voltage for non linear load is shown. It can be observed that the results present a good accordance with the standard.

Fig. 24 – Harmonic content of output voltage.

#### 6 CONCLUSIONS

In this paper a new AC voltage regulator was presented, operating at high frequency and providing energy to a linear and non-linear load. The proposed topology has performed an effective regulation of the output voltage. The harmonic distortion of the output voltage is very low (<5%). The proposed topology can also act as an active filter, compensating distortions in the input voltage.

Using the proposed converter to provide energy to linear loads, high efficiency can be obtained. However, in the case of non-linear loads this efficiency decreases significantly, because the increase of RMS current due to this load.

## 7 REFERENCES

- [1] CARDOSO, César Mauro. Estudo e Realização de um Estabilizador de Tensão Alternada a Transistor de Potência. Florianópolis, SC Brasil, 1986. Dissertação (Mestrado em Engenharia Elétrica) Centro Tecnológico, Universidade Federal de Santa Catarina.

- [2] FAGUNDES, João C. dos Santos. Estudo e Realização de um Variador Estático Direto de Tensão Alternada Senoidal. Florianópolis, SC Brasil, 1983. Dissertação (Mestrado em Engenharia Elétrica) Centro Tecnológico, Universidade Federal de Santa Catarina.

- [3] CAMPOS, Alexandre & JOÓS, Géza & ZIOGAS, Phoivos et al. Analysis and Design of a Series-Connected PWM Voltage Regulator for Single-Phase AC Sources. *IEEE Transactions on Industry Applications (RIA)*, Vol. 32, n<sup>0</sup> 6, USA, p. 1285-1292, November/December, 1996.

- [4] OLIVEIRA, J. C. & FREITAS, L. C. & COELHO, E. A. A. et al. A Half-Bridge PWM AC/AC Converter. *4<sup>nd</sup> Brazilian Power Electronics Conference(COBEP'97)*, Belo Horizonte, MG Brazil, p. 385-390, December, 1997.

- [5] BARBI, I. & FAGUNDES, J. C. & KASSICK, E. V. A Compact AC/AC Voltage Regulator Based on an AC/AC High Frequency Flyback Converter. *IEEE Power Electronics Specialists Conference (PESC'91)*, Boston USA, p. 846-852, June, 1991.

- [6] OLIVEIRA, J. C. & FREITAS, L. C. & COELHO, E. A. A. et al. A Half-Bridge PWM AC/AC Converter. *IEEE Applied Power Electronics Conference (APEC'96)*, San Jose, CA USA, p. 709-715, March, 1996.

- [7] FAGUNDES, J. C. & KASSICK, E. V. & BARBI, I. A PWM AC Chopper Without Dead Time and Clamping Circuit. 2<sup>nd</sup> Brazilian Power Electronics Conference(COBEP'93), Uberlândia, MG Brazil, p. 302-307, November, 1993.

- [8] VILLAÇA, Marco V. M & PERIN, Arnaldo. Variador de Tensão Alternada a Interruptores Bidirecionais com Célula de Comutação ZVS. *II Seminário de Eletrônica de Potência (SEP-95)*, INEP/UFSC, Florianópolis, SC Brasil, p. 125-132, Agosto, 1995.

- [9] OLIVEIRA, J. C. & FREITAS, L. C. & COELHO, E. A. A. et al. A Serial Regulator Using a Soft Switching PWM AC/AC Full Bridge Converter. *IEEE Power Electronics Specialists Conference (PESC'99)*, Charleston, South Carolina USA, p. 193-198, 1999.

- [10] BARBI, Ivo. *Projeto de Fontes Chaveadas Curso*. Florianópolis, SC Brasil, 1990.

- [11] BARBI, Ivo & MARTINS, Denizar Cruz. Eletrônica de Potência Conversores CC-CC Básicos Não Isolados. Florianópolis, SC Brasil, 2000

- [12] BATISTELA, Nelson Jhoe. Inversor de Tensão com Saída Senoidal Controlado por Modo Deslizante com Freqüência Fixa. Florianópolis, SC

Brasil, 1994. Dissertação (Mestrado em Engenharia Elétrica) – Centro Tecnológico, Universidade Federal de Santa Catarina.

- [13] FILHO, Wail Metzker Pastorelo . Controle por Modo Deslizante Aplicado a Inversores de Tensão. Florianópolis, SC Brasil, 1995. Dissertação (Mestrado em Engenharia Elétrica) Centro Tecnológico, Universidade Federal de Santa Catarina.

- [14] MELLO, Luiz Fernando Pereira de. Análise e Projeto de Fontes Chaveadas. São Paulo, SP Brasil, 1996.

#### 8 ACKNOWLEDGEMENTS

The authors would like to thank CAPES for the financial support and THORNTON, IR and SIEMENS for provide the components used on the built prototype.