# Universidade Federal de Santa Catarina Departamento de Engenharia Elétrica Laboratório de Materiais Elétricos - LAMATE

# Experiência 3 – Tensão de gate X corrente de dreno Resistências de entrada e saída Chip 2 - Transistores MOS e Circuitos Lógicos

Os ensaios sugeridos a seguir, utilizando o *chip* constituído de transistores metalóxido-silício (MOS), pretendem fornecer conceitos básicos a respeito do funcionamento destes dispositivos e demonstrar como os mesmos podem ser combinados para dar origem a circuitos lógicos largamente empregados em eletrônica. Neste primeiro experimento, deseja-se investigar de que forma varia a corrente de dreno em função da tensão de *gate*, para transistores CMOS tipo n e tipo p, bem como estimar valores para as resistências de entrada ( $R_{on}$ ) e de saída ( $R_{out}$ )

### Introdução

A tecnologia *MOS* responde atualmente por 90% do mercado mundial de semicondutores, em sua maioria constituído de memórias e microprocessadores. Seu emprego com fins didáticos se dá devido ao fato de serem elementos conceitualmente simples e de apresentarem boa correlação entre valores teóricos e experimentais, entretanto, são produzidos apenas na forma integrada, isto é, com centenas ou até milhares de outros no mesmo *chip*.

Como um dispositivo a dois terminais, o transistor *MOS* funciona como um capacitor. O contato metálico no alto do transistor é chamado *gate*. O dióxido de silício na forma ultrapura usado neste tipo de tecnologia é um ótimo isolador.

Quando uma tensão positiva é aplicada no eletrodo gate, uma carga negativa é induzida no silício, e vice-versa. Um transistor MOS é simplesmente o capacitor citado acima com dois contatos laterais no silício. Estes eletrodos são chamados fonte (source) e dreno (drain), porém o dispositivo é completamente simétrico, de modo que a identificação dos dois contatos depende das conexões do circuito. A superfície do silício que sofre inversão é chamada de canal (channel) porque fornece um canal condutor tipo p ou tipo n da fonte para o dreno. Para que haja uma corrente qualquer fluindo da fonte para o dreno, é necessário aplicar uma pequena tensão positiva  $V_d$  ao dreno.

# <u>Parte 1</u> – Tensão de gate X corrente de dreno

#### Material

- Chip n° 2

- Fonte de tensão 0 5V

- Amperimetro 0 50mA (ou multimetro digital)

- Voltímetro 0 5V (ou multímetro digital)

- Potenciômetro  $500\Omega$  ou similar

#### Prática

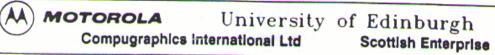

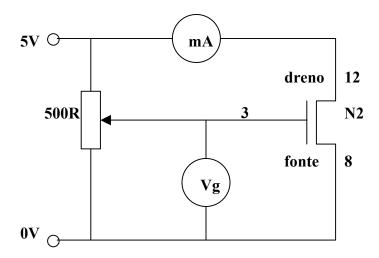

Serão utilizados para esta prática os transistores identificados como **N2** e **P2**, contidos no *chip* 2.

Conecte o *chip* com transistores MOS conforme os esquemas abaixo. Utilize o potenciômetro para ajustar a tensão de *gate* inicialmente em 0 V . Aumente a tensão gradualmente até 5 V, fazendo a leitura do valor correspondente para a corrente de dreno. Anote os resultados e esboce os gráficos.

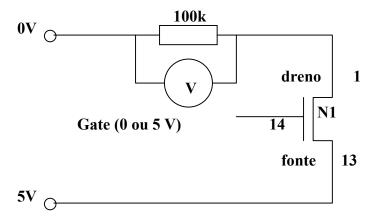

Figura 1 - Esquema para a medida da corrente de dreno em função da tensão de gate no transistor N2

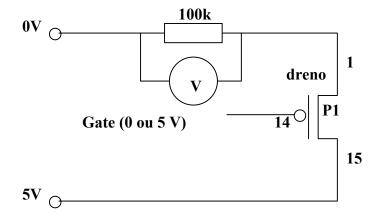

Figura 2 - Esquema para a medida da corrente de dreno em função da tensão de gate no transistor P2

#### Parte 2 – Resistências de entrada e saída

#### Material

- Chip nº 2

- Fonte de tensão 0 5V

- Resistor de 100kΩ

- Voltímetro 0 5V (ou multímetro digital)

#### Prática

Serão utilizados para esta prática os transistores identificados como **N1** e **P1**, contidos no *chip* 2.

Realize as conexões do *chip* com transistores MOS conforme os esquemas abaixo. Ligue o terminal de *gate* à saída de 0V e meça a tensão sobre o resistor. Faça o mesmo com o terminal de *gate* conectado à saída de 5V. Para um transistor tipo *n*, a resistência de entrada é calculada com a tensão de *gate* em 5V, para um transistor tipo *p*, a tensão de *gate* deve estar em 0V. Seguem as fórmulas para o cálculo de ambas.

$$\begin{aligned} \mathbf{V}_{\text{tran}} &= \mathbf{V}_{\text{fonte}} - \mathbf{V}_{\text{resistor}} \\ \mathbf{I}_{\text{tran}} &= \mathbf{I}_{\text{resistor}} \\ \mathbf{R}_{\text{tran}} &= \mathbf{V}_{\text{tran}} \, / \, \mathbf{I}_{\text{tran}} \end{aligned}$$

Figura 3 - Esquema para medida das resistências de entrada e saída para o transistor N1

Figura 4 - Esquema para medida das resistências de entrada e saída para o transistor P1

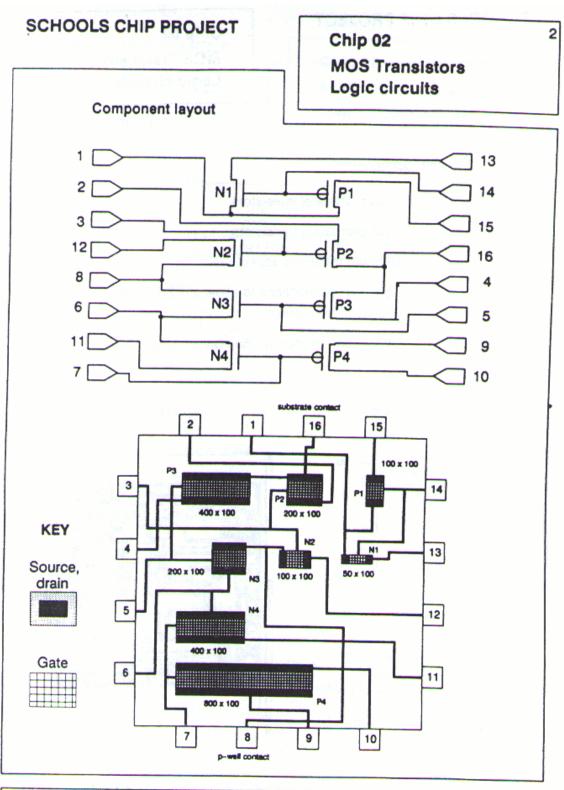

# SCHOOLS CHIP PROJECT

Chip 02 MOS Transistors Logic circuits

## General description

The chip contains:

Four n-channel transistors

Four p-channel transistors

Different transistor aspect ratios

Open pin connections to allow a large number of logic circuits to be realised

Connection modes for memory circuits

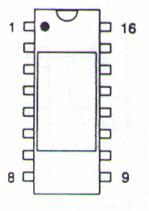

# **Package**

Ceramic dual-in-line 16 pins glass lid 0.3" wide 0.1" pin pitch

Max power rating 1 W

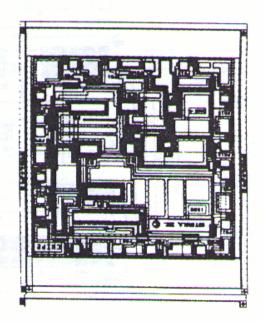

## Chip plan view

MOTOROLA

University of Edinburgh

Compugraphics International Ltd

Scottish Enterprise